# Huxelerate: Bringing Software Performance Optimization Research into the Market

July 7<sup>th</sup> 2023

Sara Notargiacomo – Co-founder and Chief Business Officer sara.notargiacomo@huxelerate.it

GLOBAL ENERGY

CONSUMPTION

Doubles every 3 years

GLOBAL ENERGY PRODUCTION

Grows by 2% a year

## Huge energy consumption might recall...

#### **Data-center on Wheels**

## **COMPUTING EFFICIENCY MUST DOUBLE EVERY 1.1 YEARS**

- Computing power 10x each next level of autonomy. L3-L4-L5 autonomy 10s, 100s, 1000s TOPS (tera operations per second)

- By 2050 95% of the global fleet autonomous

Source: MIT "Data Centers on Wheels: Emissions from Computing Onboard Autonomous Vehicles"

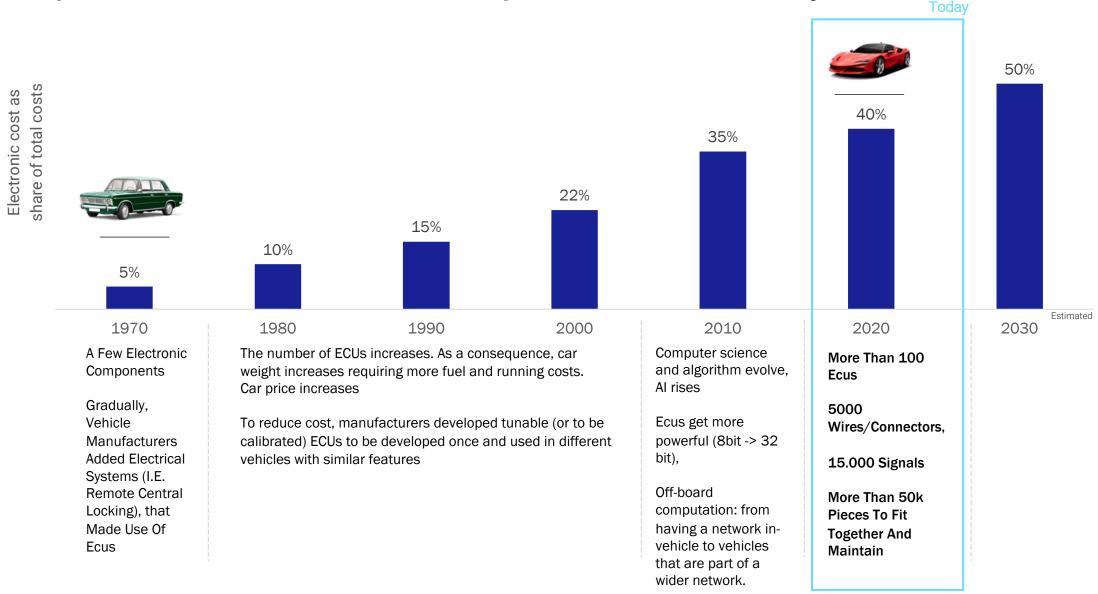

#### The explosion of vehicle electronic components in the last 50 years

Source: Statista

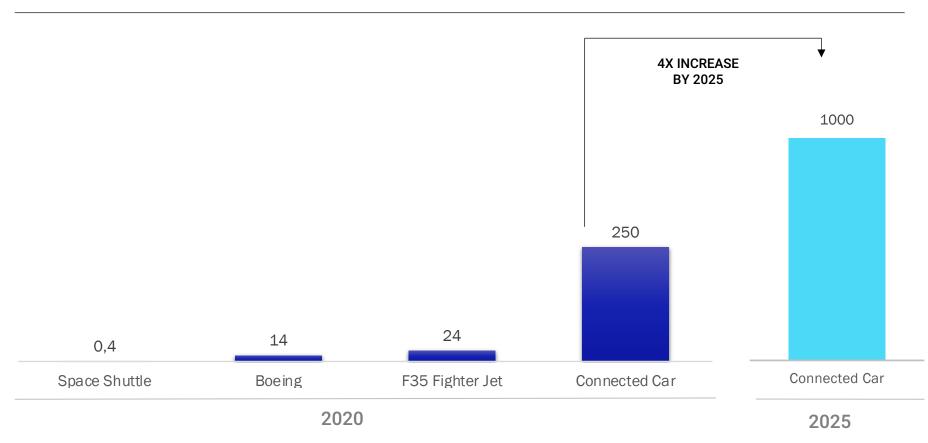

#### **Explosion of vehicle software complexity**

Source: McKinsey & Company, When code is the king: Mastering automotive software excellence. Roland Berger, Computer on wheels / Disruption in automotive electronics and semiconductor

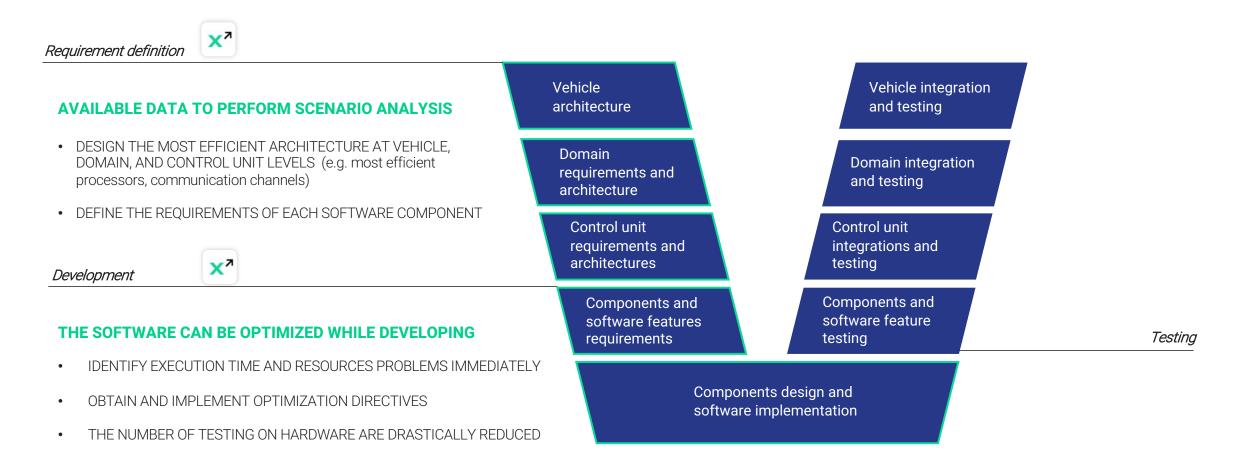

1. CORRECTLY SIZE AND OPTIMIZE THE VEHICLE COMPUTING INFRASTRUCTURE

2. ENABLE **SOFTWARE AND RESOURCE USAGE OPTIMIZATION**

# HUXELERATE OFFERS A SaaS DEVELOPMENT TOOLBOX TO SUPPORT DEVELOPERS IN OPTIMIZING VEHICLES SOFTWARE AND COMPUTING INFRASTRUCTURE

© all rights reserved

# Huxelerate automates performance estimations and optimization directives virtualizing the entire vehicle

VIRTUALIZED VEHICLE COMPUTING INFRASTRUCTURE<sup>1</sup>

#### PERFORMANCE ANALYSIS

- Estimate the current and achievable performance of software on different computing hardware

- Correct sizing of vehicles computing infrastructure: select the processors and computing hardware that maximize performance and computing efficiency, given a target cost

- Estimate CO2 Savings

## DIRECTIVES FOR OPTIMIZATION

Software performance and resource optimization: performance estimated and optimization directives to support developers in achieving the highest level of performance and optimizing usage of available resources

**HUxelerate**<sup>7</sup>

<sup>&</sup>lt;sup>1</sup> It may be any kind of vehicle: cars, motorcycles, trucks, tractors

#### Full integration into standard process and consolidated toolchains

#### Already adopted by car manufactures and Tier 1

REDUCED COMPUTING INFRASTRUCTURE COSTS

REDUCED OPTIMIZATION TIME AND COST

IMPROVED SOFTWARE PERFORMANCE

**UP TO 40%**

**UP TO 60%**

**UP TO 50%**

WHERE WE STARTED?

#### Back in 2019-2020: Hugenomic and the focus on genomics research

| The Computational Bottlenecks are due to |  |

|------------------------------------------|--|

| some common limitations                  |  |

The computational bottlenecks of genomic data analysis are generated by some common limitations:

Computational intensive

Sequencing Technologies will require around 2 trillion CPU hours by 2025

Massive amount of data

Hundreds of gigabytes of data

General purpose architecture are inefficient

The main reason is that they are designed for generic workloads, and they are not optimized for specific scenarios

<sup>1</sup> Source: Decadal Plan Abridged Report

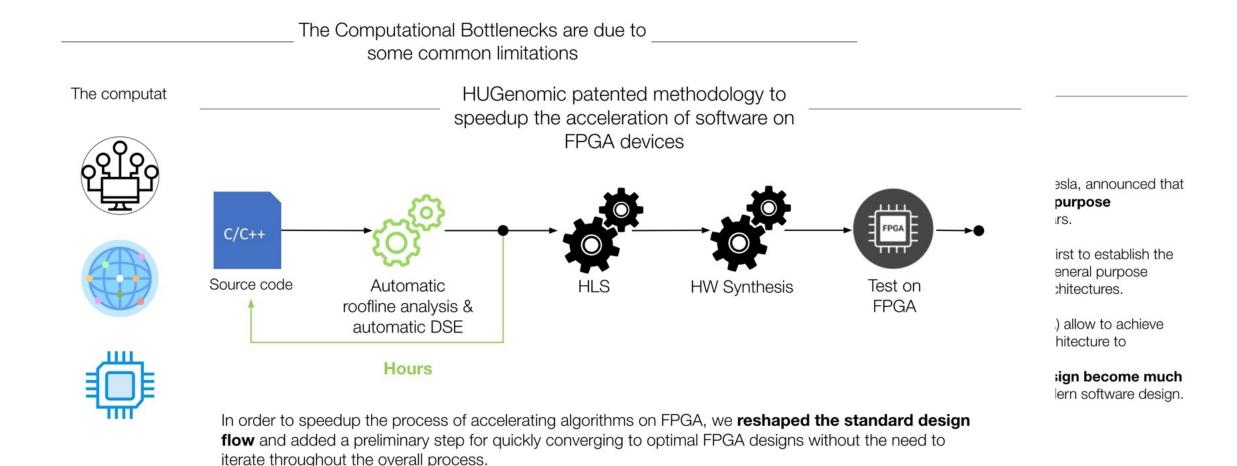

#### Back in 2019-2020: Hugenomic and the focus on genomics research

The Computational Bottlenecks are due to \_\_\_\_\_some common limitations

The computational bottlenecks of genomic data ana

HUGenonomic wants to be a key player in the transition from general purpose architectures to domain specific architectures

Computational intensive

Seque by 202

Massive amount of data

Hundre

General purpose architecture are inefficient

The many

Tesla Dumps NVIDIA, Designs and Deploys its Own Self-driving AI Chip

line. The company was relying on MVIDIA's DGX processors for Autopilot. Called the Tesla FSD Chip (fill self-driving processor has been deployed on the latest batches of Model S and Model X since March 2019, and the company looks to expand it to its popular Model 3. Tesla FSD Chip is an FPGA of 250 million gates across 6 billion transistors crammed into a 250 mm<sup>2</sup> die built on the 1 mm FIRET process at a Samsung Electronics fab in Tesas. The chip packs 32 MB of SRAM cache, a 96x66 muldadd array, and a cumulative performance metric per die of 72 TOPS at its rated clockspeed of 2.00 GHz.

A typical Autopilot logic board uses two of these chips. Tesia claims that the chip offers "21 times" the performance of the NVIDIA chip it's replacing, Elon Music referred to the FSD Chip as "the best chip in the world," and not just on the basis of its huge performance uplift over the previous solution. "Any part of this could fail, and the car will keep driving. The probability of this computer failing is substantially lower than someone losing consciousness - at least an order of magnitude," he added.

On April 23th Elon Musk, CEO of Tesla, announced that Tesla will no longer use general purpose architectures on its self-driving cars.

Such announcement is one of the first to establish the start in the architecture shift from general purpose architectures to domain specific architectures.

Domain specific architectures (DSA) allow to achieve higher efficiency by tailoring the architecture to characteristics of the domain.

This will require that **hardware design become much more efficient**, and more like modern software design.

<sup>1</sup> Source: Decadal Plan Abridged Report

#### Back in 2019-2020: Hugenomic and the focus on genomics research

¹ Source: Decadal Plan April Source

$\bowtie$

info@huxelerate.it

/company/huxelerate/

Via San Martino, 12 Milano